デジタルシグナルプロセッサ

デジタルシグナルプロセッサ(英: digital signal processor、DSP)は、デジタル信号処理に特化したマイクロプロセッサであり、一般にリアルタイムコンピューティングで使われる[1]。

目次

1 概要

2 アーキテクチャ

2.1 プログラムのフロー

2.2 メモリアーキテクチャ

2.3 データ操作

2.4 命令セット

3 歴史

4 最近のDSP

5 関連項目

6 脚注

7 外部リンク

概要

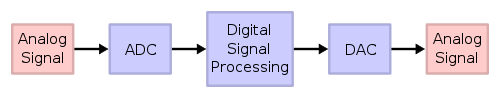

デジタル信号処理のアルゴリズムは一般に大量の演算を一群のデータに対して素早く行う必要がある。アナログからデジタルに信号を変換し、それを操作し、再びアナログに戻す(下図参照)。多くのデジタル信号処理は潜伏時間に制約がある。すなわち、デジタル信号処理がある時間以内に完了しないと、システムは役に立たない。

単純なデジタル信号処理システム

多くの汎用のプロセッサでも、デジタル信号処理のアルゴリズムを正しく実行できる。しかし、そのようなマイクロプロセッサは消費電力や大きさの関係で、携帯電話やPDAなどには適さなかった。デジタル信号処理に特化したDSPは、より安価でより低消費電力でありながら、より高性能を提供する。なお、汎用のマイクロプロセッサやマイクロコントローラでも、積和演算命令の付加など、従来DSPでおこなっていた処理を受け持つことができるものも増えている。

特定の演算処理を高速に行なうことを目的に作られ、音声処理・画像処理などに使われることが多い。レーダーなどの信号処理や無線通信回線の信号の変調・復調等でも使用されていた。DTM用音源ボードなどのPC用拡張ボードに使用されたほか、携帯電話、デジタルカメラ、デジタルビデオカメラ、電子楽器などに使用された。高速フーリエ変換のような演算を行ない、アナログでは不可能なフィルタ動作や信号情報の圧縮・変調・復調処理などを行なった。

DSPのアーキテクチャは、デジタル信号処理に最適化されている。以下では、そのような特徴を解説する。

アーキテクチャ

- 構成

- プログラムメモリとデータメモリの分離(ハーバード・アーキテクチャ)

メモリ管理ユニットを持たない。DSPはマルチタスクは可能だが、仮想記憶やメモリ保護はサポートしていない。仮想記憶を利用すると、入れ替え処理に予期不可能な時間がかかるからである。- データストリーミングのためのメモリアーキテクチャになっており、DMAを頻繁に使用する。

- 番地指定

- ハードウェアによるモジュロアドレッシングにより、リングバッファを実装した際にループで毎回境界チェックする必要がない。

- ビット反転番地指定という特殊な番地指定方式があり、高速フーリエ変換処理で使われる。

- 命令

積和演算を高速に実行できるように高速乗算器を持つ。特に整数演算の場合は積和演算器を持つものが多い。FIRフィルタや高速フーリエ変換 (FFT) といったデジタル信号処理では、積和演算の性能が非常に重要である。- 特殊なSIMD演算が可能

- 大量の繰り返し処理を分岐命令によるオーバーヘッドなしに高速に実行できる(遅延分岐方式であり、つまりディレイスロットが存在する)

プログラムのフロー

浮動小数点数演算装置は直接データパスに組み込まれている。

パイプラインアーキテクチャ- 多数の積和演算器を並列動作させることで、演算性能を高める。

- ハードウェアでループを制御し、ループ操作にかかるオーバーヘッドを低減または排除している。

メモリアーキテクチャ

- DSPのメモリアーキテクチャは、複数のデータと命令を同時にフェッチできるようになっている。以下のいずれかである。

- ハーバード・アーキテクチャ

ノイマン・アーキテクチャの修正版

Direct Memory Access を多用- 特殊なメモリアドレス計算ユニット

データ操作

- 飽和演算(算術桁溢れ、算術下位桁溢れをそれぞれ最大値・最小値に丸める)を行う。汎用CPUで最大値に1を加えると、例外を起こさない場合でも最大値ではなくなる。飽和演算モードを設定できる場合もある。

- 高速化のために固定小数点演算を使うことが多い。

- シングルサイクルの処理によってパイプラインの効率を高めている。

命令セット

積和演算命令は、行列処理(フィルタリングにおける畳み込み、ドット積、ホーナー法などの多項式計算)で頻繁に使用する。- 並列性を強化する命令: SIMD、VLIW、スーパースケーラ

モジュロアドレッシング(リングバッファ用)とビット反転アドレッシング(高速フーリエ変換用)

歴史

DSPチップが登場する以前、デジタル信号処理はビットスライスプロセッサで実装していた。AMD Am2900ファミリが特にその用途で使われていた。AMDはリファレンス設計も公開していたが、実際の個々の用途の設計はそれ専用に行われていた。ビットスライスプロセッサには乗算器チップもあり、例えばTRWのリリースした TRW1008 や TRW1010 にはアキュムレータ付きの乗算器チップもあった。そのような乗算器は積和演算には必須だった。

1978年、インテルはアナログシグナルプロセッサ 2920 をリリースした。オンチップのADC/DACを備え、信号処理部がその間にある構成であった。ただし、ハードウェアの乗算器がなく、市場でも受け入れられなかった。1979年、AMI(アメリカン・マイクロエレクトロニクス)が AMI S2811 をリリース。マイクロプロセッサ用周辺チップとして設計されており、ホストプロセッサが初期化・設定を行うようになっていた。S2811 も市場では受け入れられなかった。

1980年にベル研究所が試作品 AT&T DSP1 をIEEEの集積回路に関する国際会議で発表した。同年日本電気 (NEC) が製品としてμPD7720を発表した。これらのプロセッサはいずれも公衆交換電話網の通信の研究が元になっている。他に Altamira DX-1 という初期のDSPもある。整数パイプラインを4本持ち、ディレイスロットと分岐予測を備えていた。

1983年にはテキサス・インスツルメンツ (TI) が高性能なTMS32010を発売し、成功を収めた。ハーバード・アーキテクチャであり、命令とデータのメモリが分離されていた。ロード加算命令や積和演算命令といった特殊な命令セットを備えていた。16ビットの積和演算を390ナノ秒で実行する。TIは現在では汎用DSP市場のリーダーとなっている。他にもモトローラの 56000 も成功を収めている。その後アナログ・デバイセズ社などがこの市場に参入し、広く使われるようになった。

この頃の製品は、アナログで構成される全体システムの中の信号処理サブシステムを高性能化するために、DSPによるデジタル処理が利用された。21世紀初頭現在のようなフルデジタル環境とは異なり、この信号処理サブシステムの入力部と出力部にはA/DコンバータとD/Aコンバータが備えられていた。

約5年後、第2世代のDSPが広まり始めた。第2世代の特徴はメモリを3つ持つことができ、2つのオペランドに同時にアクセスできる。また、ハードウェアによる短いループの高速化をサポートし、モジュロアドレッシングなどのアドレッシング機能を備えた。当時の性能は平均的モデルで、24ビットの積和演算が24ナノ秒となっていた。この世代の代表例として、AT&T DSP16A とモトローラ DSP56001 がある。

第3世代の特徴はアプリケーション専用ユニットを搭載した点で、通常のデータパスで使える命令を用意したり、コプロセッサの形態で接続していた。それらのユニットは、高速フーリエ変換や行列演算とった特定の計算をハードウェアで高速化するものである。モトローラ MC68356 では複数のプロセッサコアを搭載し並列動作が可能だった。1995年以降の他のDSPとしては、TI TMS320C541 や TMS320C80 がある。

第4世代の特徴は、命令セットの変更と命令のデコードの変更である。SIMDやMMX拡張が追加され、VLIWやスーパースカラーアーキテクチャが登場した。クロック周波数も高くなり、現在では積和演算は3ナノ秒で実行できる。

1990年代には名称の元ともなった音声信号のみならず、画像や動画のような情報密度の高いものまで演算処理するようになったが、20世紀末から21世紀初めにかけて、PC用のグラフィックス・ディスプレイ用プロセッサから発展してきたGPUや、リアルな動画処理が扱える高性能なゲーム用プロセッサとして開発されたCell、そして各種のメディアプロセッサと呼ばれるもの等が、DSPで行なう積和演算処理以上の高度な演算処理をプログラマブルに実行出来るものとして登場してきたために、DSPが発展・占有しつつあった高処理能力を必要とする用途は奪われ、DSPは従来から存在し今では小さく狭くなった低処理能力の用途にほぼ限定して使用されている。GPUは2007年頃から、GPGPUという動画処理以外での処理に使用される方向へと用途が拡大されている。

Blackfinなど、マルチメディア処理向けの組み込みプロセッサにおいて、DSPコアやDSPの機能を備えるものが存在している。

最近のDSP

TI の TMS320C6000 シリーズは1.2GHzのクロック周波数で、命令キャッシュとデータキャッシュを分離実装し、8MiBの2次キャッシュを装備し、64個の(E)DMAチャネルを備えてI/Oも高速化している。上位機種は8000MIPSの性能で、VLIW型の命令を使って1クロックに8命令を実行できる。また、各種I/Oバスにも対応している(PCI、シリアルなど)。

高性能DSP市場では他にフリースケールも活発に事業を進めている。同社は、StarCore アーキテクチャに基づくマルチコアDSPファミリ MSC81xx を提供している。最新の MSC8144 DSP は4個のSC3400 StarCore DSPコアを備えており、各コアが1GHzで動作する。Berkeley Design Technology, Inc. (BDTI) が公表している BDTIsimMark2000 の結果によると、SC3400 は1GHzのプログラマブルDSPの中でも高性能を発揮している。

アナログ・デバイセズもDSP市場では重要な位置を占めている。様々なDSPを取り揃えているが、中心はマルチメディア向け(コーデック、フィルタ、DA変換など)である。SHARCベースのプロセッサは、198MFLOPS(66MHz)から2400MFLOPS(400MHz)の性能である。機種によっては複数の乗算器やALUを備え、SIMD命令や音声処理専用のコンポーネントや周辺機器を備えている。また、同社のBlackfinファミリは組み込み用DSPであり、DSP機能と汎用プロセッサの機能を備えている。そのため、μClinuxカーネルやvelOSity、Nucleus RTOSなどのOSを実行しつつ、リアルタイムデータも効率的に処理できる。

またNXPセミコンダクターズは、VLIW技術を使いマルチメディア処理に最適化した TriMedia をリリースしている。一部製品ではDSPをSoCの固定機能ブロックとして使っている。TriMedia は固定小数点数と浮動小数点数をサポートし、フィルタやコーデックに特化した命令を備えている。

多くのDSPが固定小数点数を使っているのは、実際の信号処理では浮動小数点数のような広範囲な数値を必要とせず、固定小数点数の方が高速に処理できるためである。ただし、ダイナミックレンジの広い用途では浮動小数点数が必須になる。また、一般的なコンピュータではアルゴリズムが浮動小数点数で実装されていることが多いため、ソフトウェア開発のコストを低減させるために浮動小数点数のDSPを採用する場合もある。

DSPの機能はFPGAでも実装できる。

組み込み用の汎用RISCプロセッサは、DSP的な機能を取り入れつつある。例えば、ARM Cortex-A8 には128ビットのSIMDユニットがあり、16ビットおよび8ビットのSIMD演算性能は非常に高い。

関連項目

- IBM Mwave

- 画像エンジン

脚注

^ A. John Anderson (1994). Foundations of Computer Technology. CRC Press. ISBN 0412598108. http://books.google.com/books?id=6PUH68h45BsC&pg=PA361&dq=%22real+time%22+%22digital+signal+processor%22&lr=&as_brr=3&ei=ALYlSNGNC4KKswOczZC8DQ&sig=Wt0P3ZANNvw8E5W1GzNGY5PoXfM#PPA361,M1.

外部リンク

- DSP Processor - Core-Based Wireless System Design

- Microcontroller.com

- DSP Discussion Groups

- DSP Online Book

- DSPs and VLIW

- Pocket Guide to Processors for DSP - Berkeley Design Technology, INC

- BDTi

- BDTI DSP Kernel Benchmarks Results

- The 2008 EDN DSP directory

- DSP-FPGA.com Magazine

- AR Parameter Estimation using TMS320C30

- アナログデバイセズ

- テキサス・インスツルメンツ

- フリースケール

| ||||||||||||||||||||